С момента изобретения интегральных схем на основе структуры металл-оксид-полупроводник (МОП) в начале

Давайте разберемся в этих изменениях и посмотрим, на что они повлияли в производстве интегральных микросхем.

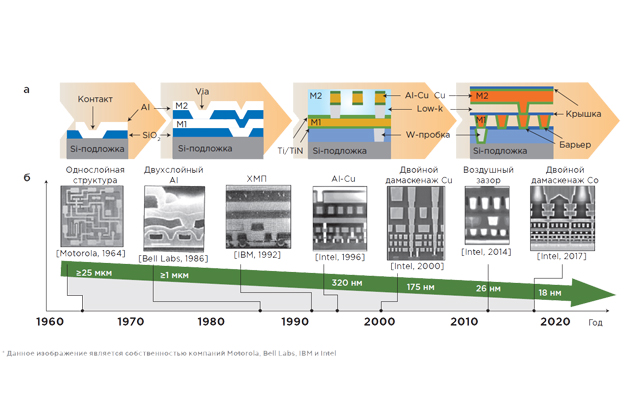

Схема эволюции технологии межсоединений и межслойных диэлектриков (inter-layer dielectric — ILD), также известной как технология back-end-of-line (BEOL), представлена на рис 1. Алюминиевые (Al) проводники, использовавшиеся в 1960-1980 годах, были заменены более качественными алюминиево-медными (AlCu), за которыми в 1997 году последовала используемая в настоящее время схема проводников с двойным дамаскеном (dualdamascene — DD) с применением меди с гальваническим покрытием. Это позволило создавать более плотные, более «быстрые» и надежные проводники и решения на их основе.

С какими ограничениями пришлось столкнутся микроэлектронному производству?

Ответ на данный вопрос крайне прост — это применение традиционных материалов при создании межсоединений меньшего размера и дальнейшего их непрерывного масштабирования. Традиционные материалы нужно было заменить, так как они стали причиной, угрожающей «жизни» закона Мура.

Несмотря на то, что кобальт (Co) недавно был представлен в качестве возможной замены материала для самых «узких» проводников из меди (Cu), чтобы продлить «жизнь» закону Мура, эти технологии, в конечном итоге, исчерпали себя, когда размеры проводни ков перешагнули предел в 20 нм. При таких критических размерах традиционные технологии — Cu и Co, а также использование благородных металлов, таких как рутений (Ru), страдают от значительных размерных эффектов в основном из-за нелинейного увеличения удельного сопротивления и результирующего сопротивления проводников и переходных отверстий. Это увеличивает задержку RC-цепей и способствует самонагреву элементов, снижает надежность электромиграции и тем самым ограничивает их токопроводящую способность и, конечно же, производительность. Кроме того, образование пустот во время заполнения металлом траншей с большим соотношением сторон (aspect ratio — AR) и сквозных отверстий во время процесса DD усугубляет проблемы с надежностью, затрудняя дальнейшее увеличение отношения размеров.

Традиционные решения не смогли соответствовать требованиям к плотности тока для нужной производительности, установленным Международной дорожной картой для устройств и систем (International Roadmap for Devices and Systems — IRDS), за пределами размеров проводников в 15 нм, что требует определения альтернативных стратегий развития слоев металлизации, чтобы «оставить в живых» закон Мура.

Что удалось открыть при использовании межсоединений из графена?

С момента своего открытия в 2004 году графен был предложен в качестве потенциального материала для будущей электроники благодаря его уникальным электрическим, оптическим и механическим свойствам. Первоначально полученный из трехмерного слоистого аллотропного графита графен представляет собой единый слой атомов углерода толщиной в атомный слой. Гексагональная сотовая кристаллическая структура графена формируется за счет sp2-гибридной связи в плоскости, возникающей в результате совместного использования электронов каждым атомом углерода с тремя ближайшими атомами углерода с исключительно высокой механической прочностью. Это приводит к уникальной электронной зонной структуре, что делает графен полуметаллом с нулевой запрещенной зоной.

Многослойный графен (multilayer graphene — MLG) предпочтительнее для проектирования межсоединений и систем по сравнению с однослойным. В первую очередь, это связано с его более низким контактным сопротивлением и более высокой плотностью состояний по сравнению с однослойным графеном. В отличие от однослойного графена MLG имеет параболическую зонную структуру, которая не только устраняет нелинейности, но и значительно модулирует его проводимость. Кроме того, сильные sp2-гибридные связи в графене/MLG обеспечивают значительно более высокую температуру плавления, чем обычные металлы, и значительно более высокую механическую прочность (сильнее, чем у стали) и плоскостную теплопроводность. Графен обладает необычайной электропроводностью в сочетании с меньшим рассеянием электронов на поверхностях и границах зерен при сверхмасштабных размерах и, следовательно, уменьшенным удельным сопротивлением на больших размерах, высокой подвижностью носителей. Высокое содержание углерода делает графен или, точнее, легированный многослойный графен — doped multi-layer graphene — DMLG, идеальным кандидатом для межсоединений на кристалле следующего поколения.

Помимо Cu, Co и Ru, некоторые другие благородные металлы (Pt, Ag, Au) и слоистые материалы (MoS2, WTe2) рассматривались как потенциальные кандидаты на межсоединения, однако они либо не могут соответствовать плотности тока, либо страдают от плохой концентрации носителей, что ограничивает их использование в будущих технологических узлах BEOL.

Что даст интеграция графеновых межсоединений в КМОП?

Микромеханическое (или жидкостное) расслоение графена из объемного графита дает относительно небольшие, микронного размера, чешуйки, которые не подходят для процесса комплементарного металл-оксид-полупроводник (КМОП).

Наиболее распространенным подходом для выращивания графена с относительно большой площадью является использование химического осаждения из паровой фазы (chemical vapor deposition — CVD), которое основано на термическом разложении его предшественников на газовой основе на металлической подложке катализатора, такой как Cu или Ni. Хотя этот подход дает высококачественный графен/MLG, он не только требует температур, намного превышающих тепловой баланс BEOL (<450 ºC), но и переноса с металлической подложки для выращивания на желаемую подложку, что делает его непригодным для прямого применения в процессе BEOL для технологии КМОП.

Другие методы выращивания графена, например, эпитаксиальный или твердофазный рост, также требуют гораздо более высоких температур, чем допустимый тепловой баланс, и полученное качество MLG недостаточно для межсоединений.

Совсем недавно Исследовательская лаборатория наноэлектроники (the Nanoelectronics Research Lab — NRL) Калифорнийского университета в Санта-Барбаре разработала новый подход к выращиванию высококачественного многослойного графена при значительно более низких температурах (~300 ºC) с помощью твердофазной диффузии атомов углерода под давлением через объем и границы зерен расходуемого металла-катализатора (Ni). MLG толщиной примерно 20 нм можно вырастить, используя механическое давление ~ 65-80 фунт/дюйм2. Время роста такой пленки составит ~ 30-60 минут.

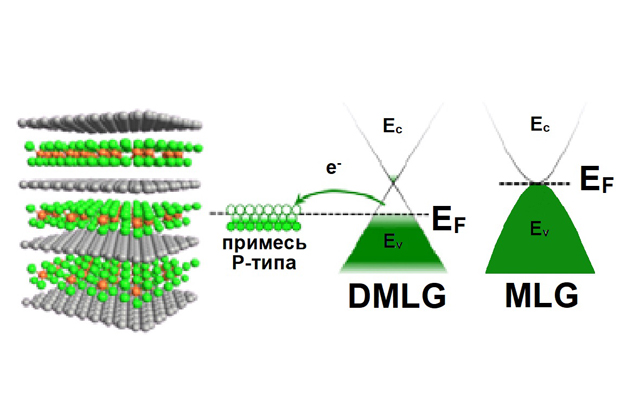

Данный метод универсален и может быть разработан для прямого выращивания высококачественного низкотемпературного графена/MLG с различной толщиной на подложках из произвольного материала. Качество графена/MLG, разработанного с использованием этого метода, эквивалентно качеству, полученному с использованием традиционных методов, что делает его жизнеспособным вариантом для интеграции в BEOL. Кроме того, введение подходящих легирующих примесей между слоями MLG (рис 2) может привести к улучшению удельного сопротивления в ~5 раз, уменьшению задержки RC в ~4 раза и увеличению энергии переключения на ~80 % на локальном уровне и на ~72 % на глобальном уровне по сравнению с обычными материалами для межсоединений.

Кроме того, межсоединения DMLG обеспечивают в 100 раз более высокую пропускную способность по току по сравнению с обычными металлами. Это делает их идеальным материалом для технологий межсоединений следующего поколения.

Все вышеописанное открыло понятный путь для интеграции графена/MLG в КМОП-технологии, а за идеей использовать DMLG последовали другие важные технологические инновации, относящиеся к межсоединениям из графена/MLG.

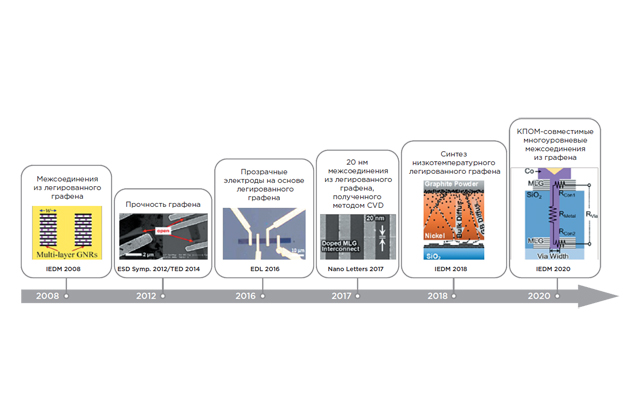

На рис 3 показана эволюция ключевых достижений в технологии межсоединений на основе графена/MLG в NRL, включая ее устойчивость к протеканию тока большой величины и электростатическому разряду, что является решением одной из серьезнейших проблем для обеспечения надежности.

Несмотря на то, что надежность и производительность одноуровневых проводников MLG были подробно изучены, ключевым требованием при применении MLG в качестве межсоединений в современных полупроводниковых технологиях является демонстрация многоуровневой системы проводников и переходных отверстий MLG, включающей контакты с низким сопротивлением. Это имеет решающее значение для демонстрации преимуществ проводников MLG при контакте с транзисторами на локальном уровне.

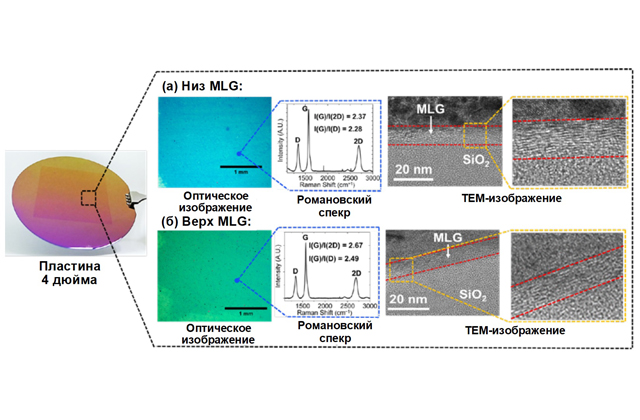

Первым шагом для достижения этого является надежное выращивание высококачественного MLG на нескольких уровнях. На рис 4 а-б показаны изображения многоуровневого графена на большой пластине с использованием КМОП-совместимого метода выращивания.

Получены практически идентичные характеристики как у MLG с нижней стороны, так и у MLG с верхней стороны, о чем свидетельствуют различные структурные и оптические характеристики как верхнего, так и нижнего уровней (рис 4 а-б). Слоистые структуры на верхнем и нижнем уровнях подтверждают универсальность метода роста для произвольных топологий поверхности.

Процесс роста, совместимый с КМОП-технологией, может быть расширен для выращивания MLG на произвольных подложках, если условия роста не приводят к термической деградации подложки. Из-за невозможности уменьшения масштаба обычных материалов барьерного и защитного слоев (TaN/Si3N4) ниже ~0,5 нм, поскольку в противном случае это могло бы привести к диффузии меди в окружающий диэлектрик, использовалось покрытие на основе графена для обычных металлических межсоединений. Оценивается и было продемонстрировано снижение общего сопротивления на 15 %. Благодаря этому совсем недавно NRL продемонстрировала BEOL-совместимый рост высококачественного MLG непосредственно на Cu, вставив слой аморфного углерода толщиной ~ 2 нм между Ni и Cu.

В принципе, при разумном выборе общих условий роста и знании относительных коэффициентов диффузии углерода в катализаторе роста и ростовой подложке этот метод может быть разработан для выращивания MLG на различных металлических (Co, Ru, W, Pt и др.) поверхностях и даже на поверхности диэлектриков.

Также текущий метод может быть адаптирован и применен для непосредственного выращивания высококачественных MLG на 300 мм стандартных пластинах, что делает его чрезвычайно универсальным и удобным для микроэлектронной промышленности.

Предел 200-летней давности преодолён! Индуктивности на основе DMLG — будущее интегральных схем

Встроенные катушки индуктивности являются важными компонентами почти всех современных электронных гаджетов — смартфонов и компьютеров и могут занимать до 50 % общей площади микросхемы. Однако в отличие от других компонентов ИС, которые уменьшаются с каждым технологическим узлом, катушки индуктивности трудно уменьшить, поскольку они зависят исключительно от магнитной индуктивности. Поэтому конструкция индукторов практически не изменилась с момента их изобретения почти два века назад.

NRL преодолела эту фундаментальную проблему масштабирования, получив значительную «кинетическую индуктивность» (КИ) в индукторах на основе MLG с легированием при комнатной температуре, что привело к получению материалов с самой высокой плотностью индуктивности из когда-либо созданных за всю историю микроэлектроники.

В отличие от обычной магнитной индуктивности кинетическая индуктивность возникает из-за внутренней инерции носителей заряда и последовательно с магнитной индуктивностью, что увеличивает общую индуктивность для данного индуктора. Легирование обеспечивает высокую добротность (до 12), в то время как КИ увеличивает общую плотность индуктивности примерно в 1,5 раза и, таким образом, впервые позволяет масштабировать индуктор.

Эта разработка имеет решающее значение для индустрии Интернета вещей (IoT) и была справедливо названа журналом Forbes «прорывом на триллион долларов».

Легирование существенно увеличивает разделение слоев в MLG, что приводит к восстановлению линейной зонной структуры многослойного графена, обладающего самым высоким КИ. Дальнейшая оптимизация процесса создания MLG и процесса легирования может обеспечить увеличение плотности индуктивности до 10 раз и открыть путь для IoT и беспроводных приложений следующего поколения.

С какими проблемами придется столкнутся микроэлектронике при интеграции и производстве графена в масштабе пластины?

Одной из основных проблем крупномасштабной интеграции MLG/DMLG в КМОП-процессы является отсутствие инструмента роста MLG в масштабе целой пластины, удовлетворяющего тепловым требованиям BEOL и требованиям процесса. Технология синтеза графена, разработанная NRL, представляет собой комплексное решение различных задач интеграции MLG в крупномасштабное производство не только межсоединений и индукторов, но и прозрачных электродов на основе графена, RFID и солнечных элементов. И, следовательно, требует более сложной регуляции температуры и давления для точного нанесения желаемой толщины графена/MLG на заданную подложку большой площади.

Помимо обычного масштабирования транзисторов и межсоединений, требования к огромным вычислительным возможностям для будущих поколений ИС требуют альтернативных архитектур. Одним из решений является 3D-интеграция или последовательноеналожение микросхем, включая материалы, устройства и межсоединения FEOL и BEOL, в вертикальном направлении, что может не только уменьшить задержку распространения электрического сигнала в межсоединениях, но и улучшить производительность, пропускную способность и энергоэффективность всего чипа.

Различные подходы, такие как сквозное соединение через кремний (Through Silicon Via — TSV), flip-chip или проволочные соединения, уже давно используются для соединения нескольких уровней в 3D-ИС. Однако их большие паразитные емкости и серьезные проблемы с электрической, тепловой, механической надежностью и адгезией, а также рост стоимости и сложности с каждым поколением серьезно ограничивают их использование для будущих технологических узлов.

Монолитная 3D-интеграция (M3D) — это другой тип схемы 3D-интеграции, в которой несколько сложенных друг в друга уровней изготавливаются последовательно на одной и той же пластине путем осаждения и рекристаллизации верхних слоев.

Теоретические исследования показали, что межсоединения, индуктивности и экранирующие слои на основе графена в сочетании с двумерными транзисторами на основе полупроводниковых материалов могут повысить плотность интеграции более чем в 10 раз по сравнению с плотностью трехмерной интеграции на основе TSV и более чем в 1,5 раза по сравнению с традиционной монолитной 3D-интеграцией. Кроме того, интеграция уровней логики и памяти с использованием M3D-интеграции может облегчить проблему вечной нехватки памяти для современной вычислительной архитектуры, открывая путь для высокоскоростной передачи данных и вычислений.

Совсем недавно была продемонстрирована сверхкомпактная гибридная ячейка памяти. Она впервые в истории, с момента начала производства резистивной памяти с произвольным доступом (Resistive Random-Access Memory — RRAM), позволила сократить количество устройств на чипе вдвое. Кроме того, она одновременно дала возможность обеспечить более высокую горизонтальную и вертикальную плотность интеграции — 3D-интеграцию, по сравнению с традиционной архитектурой, применяемой ранее. Данная гибридная ячейка может быть монолитно объединена в 3D-стеки для создания максимально высокой плотности на энергозависимых массивах памяти и нейроморфных вычислительных системах. Достигается более высокая плотность по вертикали, чем при использовании традиционной архитектуры, RRAM устанавливается поверх транзистора. Все это обеспечивает беспрецедентную производительность и энергоэффективность для имитации работы человеческого мозга в ближайшем будущем.

Таким образом, эффективные методы интеграции графена/MLG и/или других 2D-материалов со стандартными для КМОП-технологий материалами могут привести к созданию революционно новых устройств, схем и архитектур за пределами закона Мура, что откроет дверь для электроники следующего поколения.

Пассивные устройства BEOL, включая металлические межсоединения и катушки индуктивности, сталкиваются с фундаментальными ограничениями масштабирования, которые угрожают нарушить закон Мура. Новаторские изобретения ученых показали, что «правильно» спроектированный и синтезированный графен может не только помочь преодолеть самые узкие места в КМОП-технологиях, но и обеспечить беспрецедентную энергоэффективность и прирост производительности. Все это позволит продуктам нового поколения ИС выйти на новый уровень.

Таким образом, создается революционно новая технологическая платформа BEOL для будущих интегральных схем и открывается путь к проникновению графена в массовую электронику, что продлит «жизнь» закону Мура.

В статье использованы материалы:

- Chip Scale Review November — December — 2021, Sustaining Moore’s Law with graphene By Kunjesh Agashiwala, Junkai Jiang, Ankit Kumar, Chao-Hui Yeh, Kaustav Banerjee