Ожидается, что большая часть схем интеграции 3D-систем на кристалле (SoC — System-on-Chip) в будущем потребует процесса бондинга пластинапластина (W2W — Wafer-to-Wafer), который позволит напрямую соединять внутренние слои (BEOL — Back End Of Line) двух пластин в сочетании со сквозными отверстиями в кремнии, выполняемыми в конце технологического маршрута (TSV — Through-Silicon Via).

Для постоянного развития микроэлектроники и продолжения «жизни» закона Мура1 необходимо использовать совершенно новый подход, сочетающий экстремальное утонение кремния до конечной толщины 500 нм с последующим травлением наноразмерных TSV с шагом менее 500 нм. Это позволит обеспечить электрические соединения с очень высокой плотностью в рамках интеграции сети доставки энергии с обратной стороны (BSPDN — back-side power delivery network).

Что такое TSV и нано-TSV? В чем их отличие?

TSV с переходным отверстием обычно используются для соединения обратной стороны пластины с лицевой стороной через несколько микрон утоненной Si-пластины. В большинстве случаев размеры микро-TSV составляют ~1 мкм в диаметре и 5 мкм в глубину2. Для субмикронных межсоединений толщину Si-платины необходимо уменьшить, чтобы сохранить соотношение сторон TSV ниже 10:1 — типичного максимума для последующего осаждения оксида и металла. В идеале, для нано-TSV с размерами ~180 × 250 нм требуется, чтобы слой Si был тоньше 1 мкм.

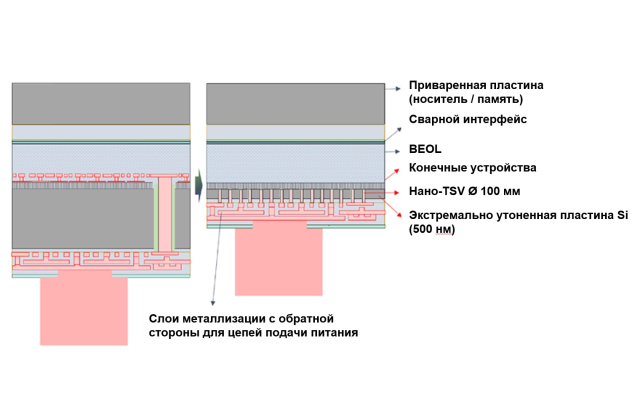

На рис 1 показаны типовые структуры устройств для микро- и нано-TSV. Последняя структура позволяет разместить все линии подачи питания на обратной стороне пластины, а более тонкий слой Si — улучшить рассеивание и отвод тепла.

Что представляет собой утонение кремниевых пластин в разрезе формирования нано-TSV?

Утонение кремниевых пластин до толщин в 5 мкм может быть достигнуто за счет комбинации шлифовки, химико-механической полировки (ХМП) и сухого травления. Из-за неоднородностей, связанных с этими процессами, окончательное изменение общей толщины (TTV — Total Thickness Variation) обычно составляет 2 мкм3. На стадии сухого травления удаляется примерно

Для достижения желаемой конечной толщины в 0,5 мкм используется комбинация сухого и влажного травления вместе со слоем, препятствующим травлению — стоп-слоем4. Высококачественный эпитаксиальный слой SiGe25% толщиной 50 нм сначала выращивается на

Следующим этапом является процесс FEOL (Front-End of-Line) в закрывающем слое Si толщиной 500 нм. Затем верхняя пластина, на которой располагаются конечные устройства, и несущая пластина соединяются диэлектрическими слоями лицом-к-лицу с использованием комбинации 150 нм SiO и 50 нм SiCN с обеих сторон.

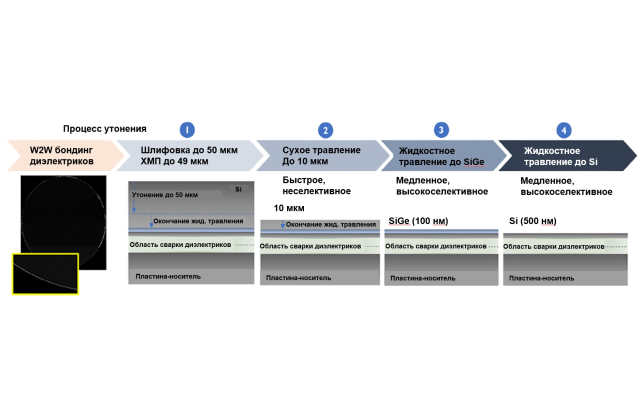

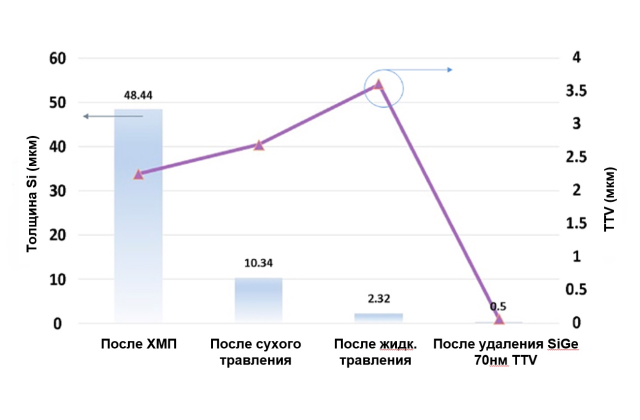

Следующая часть технологического процесса показана на рис 2. Верхняя пластина утоняется путем шлифования до 50 мкм. Шлифование механически повреждает поверхность и подповерхность Si. Поэтому оставшаяся толщина Si должна быть больше, чем толщина Si, на которую повлияло механическое воздействие, поскольку необходимо предотвращать попадание трещин и дислокаций в активные области устройств, так как они могут повлиять на производительность и надежность в целом. Затем еще 1 мкм полируется с помощью ХМП для сглаживания поверхности. На этапе сухого травления удаляется еще ~40 мкм Si, чтобы оставить 10 мкм над слоем SiGe. Преимущества сухого травления заключаются в том, что это высокоскоростной этап, позволяющий избежать любого механического контакта с пластиной. Он также дает возможность осуществлять мониторинг толщины на месте (в режиме реального времени) с помощью интерферометрии в ближнем инфракрасном диапазоне. После сухого травления оставшийся Si имеет TTV около 2 мкм. Сухое травление происходит быстро (~9 мкм / мин), но не избирательно по отношению к SiGe. Следовательно, требуется этап влажного травления, чтобы удалить оставшиеся 10 мкм Si с SiGe. Влажное травление компенсирует 2 мкм TTV, оставляя TTV у слоя SiGe на уровне ~20 нм. Селективность влажного травления Si по отношению к SiGe недостаточно высока, чтобы можно было использовать влажное травление для полного удаления Si. Цель сухого травления — подобраться достаточно близко к слою SiGe, чтобы позволить влажному травлению остановиться внутри SiGe и не нарушить его. Толщина слоя SiGe также должна быть не менее 50 нм, чтобы этого не произошло. Наконец, сам слой SiGe подвергается влажному травлению с использованием химического травителя с высокой степенью селективности SiGe к Si, обнажая эпитаксиальный слой Si толщиной 500 нм. На рис 3 показана толщина Si и TTV рабочей пластины во время процессов утонения. Окончательный Si имеет TTV около 70 нм, что идентично изменению толщины эпитаксиально выращенного слоя Si. После этого пластины готовы к проведению процессов по формированию нано-TSV.

Формирование нано-TSV

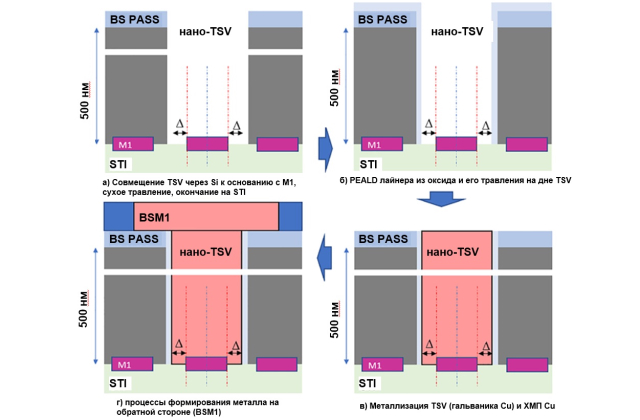

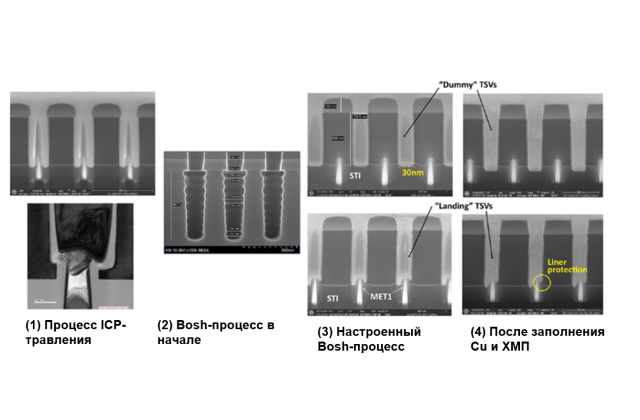

Процесс формирования нано-TSV показан на рис 4. Формирование рисунка нано-TSV осуществляется путем совмещения через Si и должно гарантировать, что нано-TSV совмещены по нижнему металлическому слою 1 (M1). Для этого требуется допуск наложения <20 нм (наложения одного слоя на другой). Нано-TSV имеют продолговатую верхнюю часть с размером ~180 × 250 нм и глубину 500 нм (конечная толщина после этапов утонения). Травление нано-TSV выполняется с использованием Bosch-процесса с очень коротким временем цикла, чтобы минимизировать «зубчатость» боковой стенки (sidewall scalloping) и облегчить последующее напыление. Травление TSV должно останавливаться на тонком диэлектрическом слое, покрывающем слой M1, поскольку это позволяет избежать повторного распыления металла во время травления нано-TSV. В противном случае могут возникнуть проблемы с надежностью конечных устройств5. После травления нано-TSV конформно осаждается 10 нм оксида (гильза или лайнер) путем атомно-слоевого осаждения, стимулированного плазмой по всей глубине нано-TSV. Затем лайнеры TSV и M1 протравливаются за одну операцию, чтобы обнажить M1. Нано-TSV покрывают барьерным слоем Ta / TaN и затравочным слоем из системы металлов, после чего заполняют все Cu и выравнивают поверхность в завершении с помощью ХМП. Наконец, формируется Cu-пробка, которая завершает металлический слой на обратной стороне (BSM1 — back side metal).

Существуют два типа TSV/нано-TSV: "фиктивные«(dummy) TSV, которые «ставятся» на диэлектрик для мелкощелевой изоляции (STI — shallow trench isolation), выравнивающие внутреннее напряжение; и «посаженные» (landing) TSV, которые подключаются к M1.

На рис 5 показаны результаты отработки процесса травления нано-TSV. Для сравнения, первоначально была предпринята попытка травления с индуктивно связанной плазмой (не Bosch-процесс), но ему не хватило селективности по оксиду, которая требуется, и обнажает M1, потому что его тонкий слой также вытравливается. Затем, если взять процесс травления Bosch, который первоначально был разработан для TSV размером 1 × 5 мкм, получаемая «зубчатость» стенок слишком велика в пределах размеров нано-TSV и значительно затрудняет их осаждение и заполнение. Поэтому Bosch- процесс был настроен в части уменьшения времени цикла (шага), чтобы получить меньший уровень «зубчатости» стенки, соответствующий размерам нано-TSV.

Какое будущее ожидает 3D-гетерогенную интеграцию с применением нано-TSV?

Интеграция нано-TSV реализует потребность микроэлектронной отрасли в поиске новых схем и разработок новых процессов. И, конечно же, это запустит новый виток развития микроэлектроники и на какое-то время продлит «жизнь» закону Мура за счет появившейся возможности дальнейшего 3D-масштабирования интегральных микросхем.

Вот только на сколько хватит данного решения и в какой срок все же придется переходить на реализацию квантовой микроэлектроники? Давайте вместе следить за развитием событий в микроэлектронном мире.

1 Журнал «Вектор высоких технологий» № 2 (52) 2021: «Шаг по направлению к квантовой электронике или жизнь микроэлектроники в эпоху постМура»

2 J. De Vos, et al., «Hole-in-one TSV, a new via-last concept for highdensity 3DSOC interconnects,» ECTC, 2018

3 A.Jourdain, et al., «Extreme thinning of Si wafers for via-last and multiwafer stacking applications,» IEEE ECTC, May 2018

4 A.Jourdain, et al., «Extreme wafer thinning and nano-TSV processing for 3D heterogeneous integration,» in IEEE ECTC, June 2020

5 S. Van Huylenbroeck, et al., «A highly reliable 1 × 5μm via-last TSV module,» IITC, 2018

6 Chip Scale Review January, February, 2021, Extreme Si thinning and nano-TSVs to advance 3D heterogeneous integration By Dave Thomas and Anne Jourdain